## SPACE COMPONENTS NEWSLETTER Mai 2020

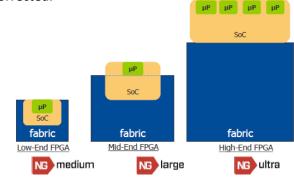

## NG medium

### NX1H35AS-FG625M & MP

- Logic 34272 LUT4+32256 DFFs+8064 CY chains

- Memory 56 BRAM Blocks of 48kb (= 2688kb), going down 36kb with EDAC activated + 168 Register Files of 168\*64bits protected by EDAC.

- 112 DSP blocks which can be cascaded.

- 1 SpW CODEC and 16 PHYs

- 16 DDR2 PHYs

- 24 clock domains splitted within 4 clock generators (CKG) including their own PPL.

- Ceramic QFP352 + LGA625 + CGA625 or for lower cost Organic PBGA625

## NG large

## NX1H140TSP-FF1752M & MP

- Logic 137088 LUT4+129024 DFFs+32256 CY chains

- Memory 192 BRAM blocks of 48kb (= 9216kb), going down 36kb with EDAC activated + 672 Register Files of 168\*64bits protected by EDAC

- 384 DSP blocks which can be cascaded

- 1 SpW CODEC and 20 PHYs

- 20 DDR2 PHYs

- 24 SERDES operating from 0,70 to 6,25Gbps allowing to comply to many protocols such as

- WizardLink

- JESD204B, ESIstream

- Serial Rapid I/O (SRIO)

- SpaceFibre (SpFi)

- Hard IP Processor type ARM Cortex-R5

- 32 clock domains splitted within 4 clock generators (CKG) including their own PPL.

- Ceramic LGA1752 + CGA1752 or for lower cost Organic Fine pitch Flip-chip 1752 balls (FF1752)

## NG ultra

#### NX2H540TSC-FF1752M & MP

- Logic 536928 LUT4+505344 DFFs+126336 CY

- Memorý 672 BRAM blocks of 48kb (= 32256kb), going down 36kb with EDAC activated

- 1344 DSP blocks which can be cascaded

- 1 SpW CODEC and 20 PHYs

- 20 DDR2 PHYs

- 32 SERDES operating up 12,50Gbps allowing to comply to many protocols

- A complete SoC named DALHIA architecture with a Quad-core ARM Cortex-R52

- Ceramic LGA1752 + CGA1752 or low cost Organic Fine pitch Flip-chip 1752 balls (FF1752)

### Protec GmbH

Rosenheimer Landstraße 117 85521 Ottobrunn-Riemerling

eMail: sales@protec-semi.com Web: http://www.protec-semi.com

# We are proud to announce the new **Cooperation with European RadHard Space FPGA Manufacturer NanoXplore**

NanoXplore is a privately owned fabless company based in France. The company was created in 2010 by three veterans of semiconductor industry with long experience in the design, test and debugging of FPGA.

Based on his team's long standing FPGA development track record, NanoXplore has designed a leading radiation hardened FPGA portfolio for aerospace, defense and industrial market.

## Low Power Rad-hard FPGA & SoCs

NanoXplore has developed Radiation-Hardened By Design SRAMbased FPGA devices for harsh environments applications.

By nature, SRAM-based FPGAs are volatile. NanoXplore has developed a dedicated architecture based on hardening techniques such as DICE (Dual Interlocked storage CEII) memory latch.

- DICE architecture has been used for Configuration Memory Cells and Internal registers (DFFs)

- **EDAC for BRAM blocks**

- TMR (Triple Module Redundancy) for all other blocks based on this hardening approach, our rad-hard SRAM FPGA are much more reliable than traditional SRAM FPGA in harsh environment.

To even further improve the reliability of our FPGA, NanoXplore has developed an advanced Configuration Memory Integrity Check ("CMIC"). CMIC is an internal scrubber controller based on a Finite State Machine with its own hardened memory block to store CRC signatures. The CMIC will constantly verify the integrity of the bitstream and any potential single errors will be detected and corrected.